Page 31 - 网络电信2023年10月刊

P. 31

解 决 方 案

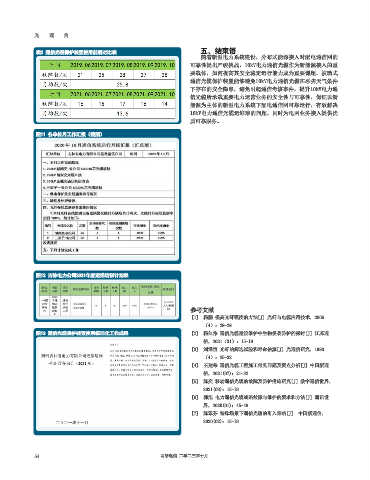

图1 系统总体架构 状态,用于关键字0xA533的插入,此状态不从FIFO中取数据。

当关键字0xA533插入完成后,状态机跳转至P_DATA状态,此时

开始从FIFO中将MAC取出并输出。在P_DATA状态中,当检测到数

据为0xA5关键字时,跳转至P_ESCAP状态,以将0xA5数据替换为

0xA5A5。当一个MAC帧传输到最后一个字节时,跳转至P_LAST1

和P_LAST2 状态,用于输出关键字0xA5F0,此状态同样不从

FIFO中取数据。最后状态机跳转至P_FIN状态,输出MAC帧最后

一字节数据。

图2 发射端链路总体架构 图4 透传组帧状态机

2.4基于Verilog的信道码块分割设计

信道码块分割模块用于将完成透传组帧的MAC帧分割为适合

可见光链路处理的码块。由于本文中采用的RS编码数据码块长

度为192字节,因此分割完成的码块长度即为192字节。同时由

于RS编码后数据长度会增加,因此必须在两帧之间插入一定长

度的间隔,以保证RS编码可顺利完成。

该模块的总体处理流程如图5所示。输入数据首先存入

图3 通道分发模块原理示意图

FIFO。该数据从FIFO中 取出后被分割成192长度的码块,分割

后的码块送入第二级FIFO。第二级FIFO中的数据由码块间隔控

制状态机取出,并在每个码块间插入30个时钟周期的间隔。同

时该状态机还受到并串转换FIFO COUNT的影响,以实现流量控

制。

2.5发射端驱动电路

为了有效补偿信道损失,针对所测得的信道特性,采用前

级预加重电路,该电路含有三级放大结构,如图6所示,前两级

共射极放大电路结构相同,主要用于实现所需的均衡效果,并

使输出信号相同,第三级则主要用于增强电路的驱动能力 [14,15]

2.3基于Verilog的透传组帧设计 。在第一级电路中,通过调整R4、R5、C2的参数,可以获得近

透传组帧模块用于在以太网MAC帧的帧头和帧尾位置插入 似如式(1)所示的增益效果。

关键字,以方便接收端根据该关键字恢复出完整的以太网MAC

帧。

图4中,以太网MAC帧的数据到达后,首先使用FIFO暂存该

数据。当FIFO中有数据时,状态机跳转至P_START1和P_START2

56 网络电信 二零二三年十月